Archive

Amanero Long Term Measurements (I)

Here are a couple of measurements for the Amanero USB board that I did for many hours. I also measured the Musiland 03US again for comparison.

- Measurement consist of counting the number of unlocks per 10 minute interval for several hours

- Connected to the Buffalo II DAC with 80 MHz clock in asynchronous operation and DPLL set to “LOWEST”

- 44.1KHz sample rate music continuously being played with the latest version of iTunes on a Windows 7 Laptop

- Capacitor mods applied (100 uF added to the input capacitors of each of the two on-board regulators) to the Amanero board

RESULTS

The first chart records the unlocks from the late night to early morning hours (click to enlarge):

Since I had removed the putty on the Crystek oscillator since I did the Musiland tests, I decided to put some mechanical isolation under the feet of the DAC case. I used pieces of gel insoles (those used for shoes).

Here are the results:

For comparison, I measured the Musiland 03 again under similar circumstances:

Note: the “burst” of unlocks in the middle of the night for the Musiland device is likely due to some “unusual event” not related to the normal working of the Musiland and BII DAC.

I also compared the power-on behavior for the Amanero-BII by consolidating the results of the 4 tests I did for the Amanero board, 1 new test for the Musiland board (Musiland 2) and the last test I did for Musiland device:

OBSERVATIONS

- Initial unlocks are pretty “well behaved” and likely relates to settling time of the clocks on both the BII and Amanero boards. The capacitor and isolation mods don’t seem to have any effect during this time which further indicates that the unlocks are caused by internal disturbances and instabilities during power-on/warm-up.

- A long stretch for several hours with zero unlocks is definitely possible with this board. This indicates that unlocks outside of this area (and with the exception of the war-up period) seem to be caused by external disturbances such as electrical and mechanical noise.

- I did not do a long term test without the capacitor mod (too impatient to try modding the board :-)), but I do believe the board responds well to this mod.

- As the second long term test shows, adding mechanical isolation also seems to help reduce some of the unlocks.

COMPARISON WITH MUSILAND

- During warm up, the Amanero board settles at a faster rate compared to the Musiland board. The multiple tests show that each board has a “signature” warm-up behavior.

- Perhaps the lower complexity of the Amanero board allows it to “settle” faster than the Musiland device.

- The Musiland looks cleaner (less unlocks) after the warm-up period. Notice the number of unlocks during the morning hours.

- Around 4:30 AM I was awaken because the volume had increased from around -60 db to -35 db …by itself! The IR sensor/Arduino got affected to such a degree that the software thought a valid code was generated by the IR receiver (the code only responds to valid codes). During that time, the DAC experienced a series of unlocks as recorded in the graph. I would consider this an anomaly and not the regular behavior of the Musiland/BII combo.

DOESN’T QUITE MAKE SENSE

The observed behavior doesn’t quite make sense. I would have expected that the Amanero board would test “cleaner” -less unlocks after warm-up, but this was not the case. The Amanero board does the one thing I thought Musiland compromised: namely deriving the clocks from discrete oscillators. The Musiland, on the other hand, derives the clocks in the FPGA’s DCM’s (from the clock signal that is passed down by the USB receiver), which results in higher amounts of jitter.

Further, the Amanero power section uses Ultra low-noise linear regulators (ADP-150) whereas the Musiland uses what appears step-down switching regulators.

Adding Input Capacitors to the Amanero Board

Continuing from the previous post, I decided to consider some mods to improve its performance. Looking at the schematics [schematic 1][schematic 2], the input capacitors to the regulators are implemented as per-spec at 1 uF in value. I decided to add a larger capacitors to both of the regulators. Used 100 uF Oscons mainly because I had a bunch of them handy. Furthermore, using large input capacitors for regulators seems to be a “normal” thing to do for audio applications. Look at the Buffalo II board use of 100 uF OSCON SVPs as input capacitors into its 3 LT 1763 on-board regulators:

For the Amanero board 3.3v regulator, I added the capacitor to the first capacitor in the PI network (C27). This further improves the filtering of the USB power. C27 is a “mere” 4.7 uF. At first I thought it was 47 uF and wrongly thought that it provided good filtering… maybe good but not as good as adding a 100 uF :-).

For the 1.8v regulator, I paralleled the 100 uF capacitor with its input capacitor (C31).

For C27, it was convenient and easy to piggyback the 100 uF capacitor. First add some solder to the pins of the capacitor, “mount” it to C27 and reheat the pins

For C31. the capacitor is too small (for me to work with), but there is a nearby ground via where I installed the (-) lead; for the + lead, I scratched off the solder mask in the power trace into the regulator, and soldered it there.

Doesn’t seem like a good solder joint since I only scratched a tiny bit of the solder mask but I tested it by wiggling it and measuring the continuity with the power input pin of the regulator.

RESULTS

The results are very encouraging. No longer do I see a “lingering” low level unlocks. The number of unlocks settles to zero after about one hour. In addition, the number of unlocks decreases at a faster rate than the Musiland, at least in the two tests I’ve done on the Amanero board.

Here is a plot of the results (44.1K sample rate, DAC DPLL set to “LOWEST”):

The test shows that the Amanero board, with the additional input capacitors performs as good, if not better than the Musiland 03 board. Same disclaimer applies: I’ve done just two tests…

For those interested, this is how I count the number of unlocks: [link]

-0-0-0-

(Update 9/25/12)

Decided to another tweak before doing a “long term” measurement: adding a small value capacitor to the USB power line.

There is currently a 4.7 uF capacitor on the USB power line. I have already added a 100 uF capacitor.

Adding .022 uF film capacitor seems to be a good idea in order to provide further bypass to the input power line. The capacitor can be installed under the board across terminals 1 and 4 of the on-board USB connector (top of the diagram is the connector side)

Now we have the following add-on capacitors to the USB power line:

RESULTS

Hmmm… Some “disturbances” in the morning hours. The last test I did on the Musiland, was cleaner. (Usual disclaimer… small number of tests…)

I did remove the piece of putty I had put on the top of the Crystek oscillator. Perhaps the problem is compounded by the vibrations? Maybe I should work on damping and mechanical isolation.

Amanero vs Musiland

Finally hooked up the Amanero USB board to the Buffalo II DAC (80 Mhz). Managed to nicely install a ribbon cable matching the input arrangement of the BII board and not having to cross any wires which can potentially create interference and noise. One wire, the data wire, has to cross over but it does so over the ground plane of the board.

Here is a close up of the wire arrangement. Every signal wire has adjacent ground wires. Most of the inner row of connectors are ground. I utilized 3 of the connections for the 5 ground wire lines. Only the actual GND wire connects to the BII board)

Connecting to Buffalo II DAC. I salvaged the wire from some board. The connector proved very useful and convenient.

MEASURING UNLOCKS

Also measured the unlocks right after power-on and compared it with the latest set of data I obtained from the Musiland 03US. In both cases the DPLL was set to lowest and the sample rate was 44.1KHz. Here are the results:

I would say the two interfaces are about even with respect to “jitter that matters” to the Buffalo II DAC. Even though the number of locks with the Amanero board seems to decrease rapidly after the first 10 minutes as compared with the Musiland board, there remains a low level of unlocks whereas the Musiland “settles” to about zero unlocks after the first hour. Of course this is just one set of data…

Several previous experiments with Musiland did show settling down to zero unlocks after about 1 hour. I continued the measurements with the Amanero board and the values are: 1:40- 6 unlocks, 1:50 -3 unlocks, 2:00 -3 unlocks. I don’t know what causes this remaining low level of unlocks. For one thing the data for the Musiland was taken a long while back, so noise in the power lines (feeding my house) might have changed. Further the driver for the two devices are rather different: the Musiland driver is a USB bulk driver whereas the driver for the Amanero board is a USB asynchronous driver.

Though the design of the Amanero board is indeed “better” than the Musiland with respect to minimizing jitter, the combination of the Musiland driver and h/w implementation seems to enable the Musiland devices to be competitive with the best USB interfaces.

AMANERO USB – I2S Interface

Just received the package in the mail. (I ordered before the GB. It took about 18 days to arrive). Here are some photos

Group buy is here: [link]

Amanero Combo 384 (click to enlarge)

The audio clocks

The logic clock

The local ADP-150 ultra low noise regulators

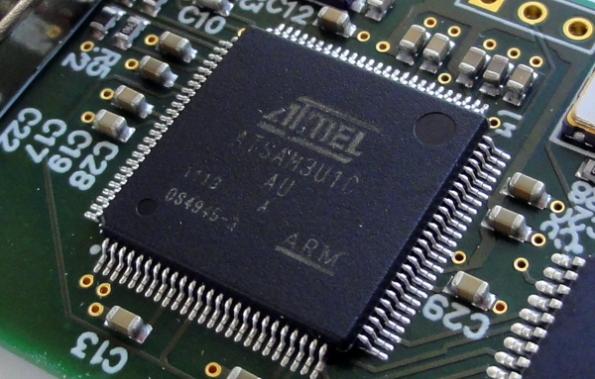

The Xilinx CPLD

The Atmel ARM microprocessor

Output connections

The firmware update port

Size comparison (click to enlarge)

C27, L1 and C1 forms the PI (CLC) filter for the USB 5V power line. You could piggyback a larger capacitor on C27

Backside of board

Can there be a standard pin arrangement so boards can just plug-in to each other?

One more (click to enlarge)

More information in my previous post [link]

New Musiland Mac Driver

There is a new Musiland beta driver for Macintosh: http://dl.musiland.cn/beta/: MlCyMon.pkg

The previous version was released in February but it did not work (invalid license).

Unfortunately, I still get “license invalid” with this version. I had already obtained and applied a new “license” to the 03US once after purchase when attempting to install version 2.3.0.0 Windows driver. Not sure if I need to get another license update, but I requested one nonetheless.

The UI has been updated. Follow the instructions here [link] to install.

The latest version of the Windows driver, v 2.4.0.0 also gives a “license invalid” message with the version of the hardware I have.

Teensy 3.0 (with I2S Interface) -Build your own SD-Card Transport?

(Update 4/16/14): The audio library was released in January 2014. Discussion here [link]

(Update 11/15/13): Discussion on gathering requirements for an audio board: [link]

(Update 9/13/12): This board has been designed with audio in mind.

I posted a question to the designer of the board:

For good quality audio applications, the I2S capability got my attention. Perusing from the chip documentation, there is support for getting the I2S master clock from an external clock (rather than derived from the system clock). Does Teensy support this capability? Thanks.

This was his answer:

@hifiduino – The I2S with DMA, and USB host, were the major factors why I waited for this chip, rather than going with one of the many NXP parts that are appearing as ARM-based projects lately. The chip can accept external clocks. It also has options to sync both transmit and receive to the same clock and frame sync pulses, so you can get both input and output using only 4 I/O pins, plus 2 more I2C to configure it.

In fact, for the audio shield I’m planning, I have a codec chip in mind that has a configurable PLL to create all the necessary clocks. I really don’t like to promote “vapor”, so at this point I’m not going to comment much on those audio shield plans, other than I definitely do have something in mind. Realistically, it’ll probably be 2-3 months until I really work on that shield and audio processing libraries.

I think we can expect good things (for audio) from Paul Stoffregen for this board

–0–

New Arduino-IDE compatible development board from the Teensyduino people (the company is officially called “PJRC”)

You can reserve one now for $22

Specifications:

- 32 bit ARM Cortex-M4 48 MHz CPU (M4 = DSP extensions) Kinetis MK20DX128VLH5

- 128K Flash Memory, 16K RAM, 2K EEPROM

- 14* High Resolution Analog Inputs (13 bits usable, 16 bit hardware)

- 34* Digital I/O Pins (10 shared with analog)

- 10 PWM outputs

- 8 Timers for intervals/delays, separate from PWM

- USB with dedicated DMA memory transfers

- 3 UARTs (serial ports)

- SPI, I2C, I2S, IR modulator

- I2S (for high quality audio interface)

- Real Time Clock (with user-added 32.768 crystal and battery)

- 4 general purpose DMA channels (separate from USB)

- Touch Sensor Inputs

More here: [link]

The I2S interface is part of the audio capability provided by the processor. The main chip is Freescale’s “Kinetis” K-series. The application note “Audio Output Options for Kinetis” describes the audio path capabilities of the chip:

In theory one can put together an SD-card transport with I2S output. Hopefully some good programmers will take on the project and share the code. If the Teensy people would provide sufficient functionality in the libraries, then anyone will be able to develop a transport

CLOCK CONSIDERATIONS

The “An I2S Application for Kinetis” document describe the I2S interface and where the clock can be derived:

Section 3.1 describes the selection of the the clock source

In order to use the I2S module, first of all, configure the clock for this module. If I2S is working as a master, the clock source of this module must be decided by setting the I2SSRC field in the SIM_SOPT2 register, or SOPT2[I2SSRC]. The possible options include:

- Core/system clock divided by the I2S fractional clock divider

- MCGPLLCLK/MCGFLLCLK clock divided by the I2S fractional clock divider

- OSCERCLK clock

- External bypass clock (I2S_CLK_IN)

The user can choose one from the above list according to the requirement.

The obvious choice would be “External bypass clock (I2S_CLK_IN)”

Maximum I2S Master Clock frequency

- According to the Reference Manual page 144, the maximum frequency for the I2S master clock is 25 MHz.

- According to the Technical Data Sheet page 20, the maximum frequency for the I2S master clock output is 12.5 MHz in VLPR mode (Very Low Power). There is no I2S clock spec for normal run mode in this document.

More on iTead TFT Display

I’ve been seeing more interest in using a graphic TFT display as interface for Buffalo DAC controller.

Here is an example implementation from reef hobbyists (salt-water fish tank people :-))

Code is here: [link]

Discussion is here: [link]. Should be a good place to get ideas and programming tips.

I’ve also updated my post on the TFT display [link] with information on the later version of the display shield.

Easy Arduino Control from your iPhone, iPod Touch

Here is an easy to implement solution to add a phone-based remote to your Arduino project:

Add a “BLE” Shield from “RedBear Labs”

Download the Arduino IDE component from the RedBear website

Download the App from iTunes

Granted, this first version of the APP is kind of very basic, you can only turn pins on/off. For something like emulating a volume knob, you will need something that will generate pulses. I am sure more features will be added to the App interface

The TPS7A47 Eval Board

Just got in the evaluation board for the new TI ultra low noise regulator, the TI TPS7A4700

I would consider this a real bargain for audio diy at $20 including shipping. In came in a huge box and it was shipped Federal Express in an even bigger box. I think TI should cut the shipping cost and pass the savings to the customers. But I suppose it is more important for business customers to get it on time and without damage than saving a few bucks.

Here are some photos

Here are the packaging and shipping boxes. I did a quick check on on the FedEx site for shipping cost for a FedEx box: $17.67. You are basically getting the board for free!

Data sheet of device: [link]

Data sheet of Eval Board: [link]

OUTPUT VOLTAGE SELECTION

Output voltage selection is done by shorting jumpers. The resultant output corresponds to the addition of the internal voltage reference (1.4 v) and the voltages indicated by the jumpers.

The board clearly labels how to select the output voltage:

Internally, the jumpers just change the value of the voltage divider resistor as shown by the diagram below. Certainly much cheaper than implementing a potentiometer.

NOISE

The TI “7A47” has half the RMS noise as the ADP-150 at 4.17 uV RMS. (The dotted blue line is the noise plot for a 5V LT1763. Compare that to the noise plot for Vout=5v -blue solid line)

Compare the above noise plot with that of the ADP-150 shown below

Modding Clocks in USB-I2S Board?

(Update 9/12/12): Updated adding RMS values to be straight addition). Peak to peak values add as root of sum of squares; RMS values add with simple addition (Xilinx)

(Update 9/3/12): Updated adding RMS values to be square root of sum of squares

We diy-types can leave any product alone. Soon after receiving the device we feel the urge to open the device and improve it 🙂

A reader asked about the wisdom of replacing the local oscillators with Crystek 957 types for the Amanero board. Keep in mind that two 957 clocks cost more than the board itself at the group-buy price.

Decided to some looking. This is what I found:

JITTER SPECIFICATION in DATASHEET

The output clocking device in the Amanero board is a Xilinx CPLD but the datasheet does not say anything about jitter in the clock circuitry. The closest cousin to that device is the Xilinx Spartan 3 FPGA which is used in many similar devices. The datasheet specifies a minimum jitter number of 150 psec peak-to-peak for clocks that are integer divided (as is the case to generate for example the bitclock or the LRclock). Keep in mind that this is added jitter by the FPGA.

Additional information:

From a Xilinx engineer [link]:

…Any clock, once it is inside the FPGA, will have roughly 100 ps peak to peak jitter imposed on it from all the internal switching that is going on, in the best case. If you have poor bypassing (decoupling), and poor signal integrity, that number can easily reach 1000 ps…

I am presuming that your 1ps source clock is 1 ps RMS, which is pretty darned great, which translates to 15 ps P-P (1ps RMS ~~ 15 ps P-P). As all jitter for Xilinx clocking is done in P-P jitter

Thus 1 ps RMS = 15 ps PP

And 150 ps PP ~ 10 psec RMS

(Note: after realizing that the FPGA people specify jitter as peak-to-peak values, I revised the FIFO reclocker post)

JITTER ESTIMATION

- We have the added jitter from the CPLD which is about 10 ps RMS (the oscillator outputs are connected to the CPLD and the master clock comes out of the DPLD)

- Then we have the jitter from the clocks which is about 2.4 ps RMS

- How about the jitter from the source? It seems to me that the jitter from the source will be nullified by the (asynchronous) re-clocking by the CPLD and does not propagate downstream. (If I am wrong, please post a comment)

Therefore, the theoretical minimum jitter value of the device is:

~ 12.4 ps RMS or 186 ps PP

(Actual calculation because we are adding RMS values we just use straight addition: total jitter=10+2.4 =12.4 )

and this is without counting any additional added jitter due to board layout, PS noise, etc. -Although the Amanero simplistic approach and the use of ADP-150 regulators would keep this to a minimum.

MODDING THE CLOCKS?

(Photo of the clocks are from Ian’s FIFO thread at diyaudio)

Is it worthwhile to replace the clocks with Crystek CCHD-957 clocks?

If we compare the jitter contribution between the CPLD and the on-board clocks, we find that the dominant component is that of the CPLD (plus any amount added by other factors such as PDB layout, PS noise, etc). The most you can eliminate is about 2 ps RMS out of a minimum of about 12.4 ps RMS or more. Not much of a change. But you’ll be the judge…

Latest Comments