DIYINHK Isolated XMOS USB Interface

DIYINHK has developed a new version of the XMOS-based USB to I2S Audio Interface. This version provides isolated I2S signal lines. Plus it uses superior oscillators.

You can read about the older version here [link]

ISOLATOR

The Isolator chip is the Silicon Labs 8661 Low Power 6-Channel Digital Isolator [link]. This is the newest device from Silicon Labs. It is based on RF coupling [link]. Apparently the Si-Labs isolators are the lowest cost ones [link]

Si86xx enhancements include:

- Schmitt-triggered inputs for higher input noise immunity

- Increased ESD protection

- High noise rejection linear regulators to ensure quiet bias voltage

- Lower power oscillators for greater operating efficiency and faster output buffers with tightened 50Ω source impedance for better matching

- Compared to competing digital isolators, Si86xx products provide near zero EMI emissions

- Industry’s highest data rate (150 Mbps) across the widest temperature range (-40 to 125 ºC) and low power operation of <1.6 mA per channel at 1 Mbps.

The “clean” side of the isolator requires a separate power supply which must be provided for proper functioning. You need to provide a 5-16V supply. This will be further regulated by a low noise regulator.

OSCILLATORS

According to DIYINHK, this version uses NDK NZ2520SD Ultralow phase noise oscillators from Japan. There are 3 oscillators: the 48 MHz for the digital circuitry of the XMOS device, the 45.158MHz and 49.152 MHz for the audio frequencies.

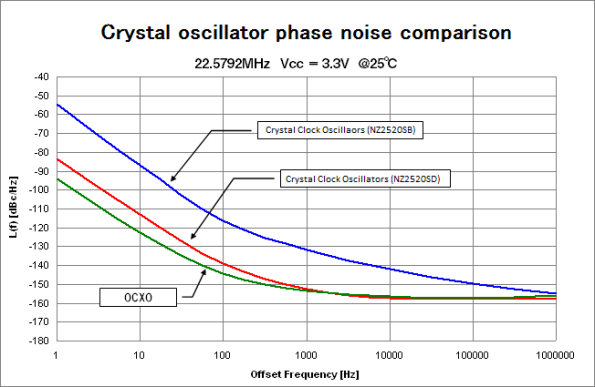

NDK has some general information on their oscillators, including jitter data here: [link]. Below is the phase noise plot of the NDK oscillators. Note the phase noise curve of the “SD” models.

NDK’s NZ2520SD low-phase-noise crystal oscillator has phase noise characteristics superior to those of the general NZ2520SB model. The company’s high-accuracy crystal oscillator (OCXO) has even better phase noise characteristics near the reference frequency.

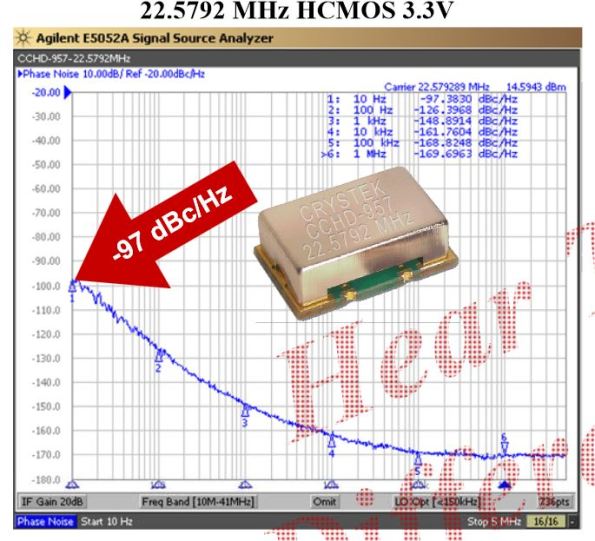

Here is the phase noise plot of the Xpresso oscillators used in the previous version

And here is the phase noise plot of the CCHD-957. Note the phase noise value of the CCHD-957 at 10 Hz (-97) vs the phase noise value of the NDK oscillator at 10 HZ (-113)

MASTER CLOCK

The Master Clock is available straight from the NDK oscillators or at the appropriate scaled-down frequency through the output pins.

Straight from the oscillators (45.158MHz and 49.152 MHz) through a U.FL socket:

Through the output pins (22.5792Mhz/24.576Mhz).

The “C7424Z” device is used as a clock divider to generate the 22.xx and 24.xx frequencies used by XMOS device and also used by the downstream device (the DAC). Seems the clock line to the XMOS device is also isolated in order to prevent any kind of noise leakage from the XMOS/USB side to the Clock/Clean side.

Note that there is no “re-clocking” of any of the I2S signals. However, Xout can be used to control an external re-clocking board for the I2S lines.

COMPLETE ISOLATION

As we’ve seen, the “clock section” including the I2S signal lines is isolated from the “XMOS/USB section”. The master clock line generated by the local clocks that connects to the XMOS device is also isolated. The two sections are powered independently.

On the backside of the board, we can see that the ground planes are also separated between the “clean side” and the “dirty side”:

USB POWER

The XMOS side (or “dirty side”) is powered by USB by default. Just like in the earlier version, the USB power can be bypassed by removing the FB1 ferrite and external 5V power can be applied through the external power connectors.

REPROGRAMABLE

For the advanced DIY’er, the XMOS device can be reprogrammed with different firmware. This can be accomplished through the CN6 connector (which is the JTAG interface for the XMOS chip):

The following device from XMOS, the xTAG-2 [link] can used to upload new firmware to the XMOS device (updating firmware through USB is not enabled in the default firmware). The xTAG-2 provides a high speed, low latency bridge between USB on the host and fast JTAG connection (up to 10Mbps) on the target.

JTAG enables the transfer of data into non-volatile device memory (uploading firmware).

There are 20 pins in this device because the device is also a debugger. The JTAG interface pins are specified in the hardware manual [link]

Sooo, why i would choose this one instead of Amanero, or WaveIO?

You like to experiment with different interfaces? :-). This one exposes the jtag interface so you can burn your own firmware (or the version available from XMOS)

Good point, also this one is cheaper. Lets focus on I2S: had anybody compared them? I’d rather do some research, before spending lots(dollars are expensive here) of money 😉 Personally I have good memories with DIYINHK(CM6631A, ES9023).

So according to Silicon Labs datasheet for Si8661 (http://www.silabs.com/Support%20Documents/TechnicalDocs/Si866x.pdf), the eye diagram showed 350ps of jitter while fed by Anritsu (MP1763C)Pulse Pattern Generator (http://downloadfiles.anritsu.com/Files/en-AU/Manuals/Operation-Manual/MP1763C_W1848AE_opm_e_9_0.pdf).

The pulse pattern generator has a spec of 20ps P-P jitter. Does this mean that the isolator added roughly 300ps of jitter? If true, it would totally negate the benefit of the good clocks on the board.

You are right about the jitter numbers of the isolator. Since they are period jitter, the phase noise jitter (the number quoted for clocks) is 300/10 or 30 psec. I don’t know whether the isolator would “totally negate the benefits”, but system wide, the clock part is totally isolated from the “USB/XMOS” part. I have used the IL isolator in the past and I did not find negative effects (in listening or in my crude “jitter measurement”).

Ah, thank you. The IL71x isolators does seem to have lower jitter number(100ps) spec. Also maybe I missed the point to begin with. If the I2S signal’s jitter is mostly defined by the two NDK clocks, how much impact does the isolator’s jitter have on the jitter of the final output? Can you shed some light on that?

Thanks for recommending the NZ2520SD, it’s a step up from Si570 re-clocking the Amanero.

Bought one of these and I don’t think you need worry about the jitter from the isolator. The output from the Xmos chip has +-2.5nS jitter from the processor clock clocking out the I2S signals. So to get any reasonable results you need to re clock the I2S signals with the MCLK.

I have been trying to re-program the board. Not too easy. I have found you need to run the jtag clock at a lower rate than standard to get the program to load. I am wanting to convert this to an input board rather that an output to use as an input from a Sabre32 ADC. Need a good input to make measurements. The jtag pin out I got from DiyInHK was not correct.

Thanks for sharing. At some point I would want to try programming this device as well. Do you have the correct jtag pin out?

The pin out is

Pin 1 Gnd

Pin 2 MSel -> Pin 3 on XTAG

Pin 3 TMS -> Pin 7

Pin 4 TDI -> Pin 5

Pin 5 TCK -> Pin 9

Pin 6 RST -> Pin 15

Pin 7 TDO -> Pin 13

Pin 8 Debug -> Pin 11

A couple of images can be found here

http://www.squarewave.co.uk/SWT_pages/DIYINHKIsolated.htm

If your interested in the Xmos code to reproduce the basic functioning of the board I will create a link to it.

Thanks… yes, I would be interested in the code.

Is the 2.5ns jitter still accurate for the latest XMOS chip that is implemented in this DIYINHK board? The latest measurements / information about this subject is more then 3 years old.

Any information regarding this subject is welcome!

Yes, there is definitely 2.5nS jitter on all the outputs from the latest Xmos chips when the Xmos example program is used as the basis of the design. I have read in one of the Xmos documents that there is jitter on the outputs but cannot find the paragraph at the moment. The reason for the jitter is that the outputs are clocked by the main processor clock – 500MHz. There is no re-clocking or latching against the MCLK. This results in +/-2.5nS jitter. The Xmos processor data sheets suggest that it may be possible to use the MCLK for the clock source for the BCLK and LRCLK. This is not done in the reference design and not in the DIYINHK board. So to get good stable LRCLK BCLK and DATA they need to be routed through D type latches clocked by the MCLK.

NDK looks interesting.. I’ve used cheap FOX 😦

I think best way is XOs located close to DAC chip (after isolator, eg. IL717). Reclock of I2S should not be needed for oversampling delta-sigma DACs because they have internal reclock on I2S bus from MCLK

for example my little diy dac have XOs close to PCM1794 http://luta.7u.cz/images/DAC2/PCMDAC3.jpg

Hello Hml i need to supply my dac uses Amanero driver which also has a dsd input over hdmi which goes straight to the dac chip. I want to build a compter with ssd or hdd drive to play files to the dac. I was thinking of using the OEM Combo384 Module – USB class 2 to I2S 32bit and DSD output Adapter then work my way back from there. I can not carry out this work myself although i have a tech guy who can build but has limited knowlege of building a computer specifically for audio.

I am thinking of using audiophils optimizer which pretty much works in dos/linux.

Any advice on build and software.

Thanks Gary

My thinking is that through USB, It doesn’t matter much what is upstream 🙂

Unless there is something not bit-perfect with the s/w such as dropping data, re-sampling, volume control, etc.

Hi HML, thank you for your great input ! Any extra information that you could provide me and the other blog readers, for the implementation of your suggestion would be much appreciated. If you know of any XMOS boards that got this kind of implementation, then please provide this blog-item with these examples. Thanks again!

Here is a link with jitter measurements on the XMOS: http://www.fetaudio.com/archives/1440

It shows jitter values of ~ 800 psec.

I would expect that any clock signal going through some complex logic would result in several 100s psec of added jitter. 800 psec is kind of in the high end of added jitter; 2.5 nsec jitter is unexpected.

I found the reference to the 2.5nsec: https://www.xmos.com/en/published/usb-audio-software-design-guide (p25)

There it says that it is added to the SPDIF output when the master clock is “resampled” t the SDPIF clock domain (eg 44.1K, 96K, etc)

in page 20, it talks about I2S:

This seems to imply that data is clocked by the derived clocks which are divided from the master clock. The expected added jitter from this kind of operation is “hundreds” of psec.

However, there is a discussion of the added jitter to the I2S lines here [link].

And according to this doc [link], the input clock (say the 24.576MHz clock) is sampled to the internal processor clock. Meaning that the external clock ticks (or transitions) are mapped to the processor clock ticks. This means that the worse “jitter” is when you just miss the external clock transition and must wait for the next internal clock tick. So the worse deviation from the actual frequency is the period of the processor frequency, thus for a 400MHz internal clock part, it is 2.5nS. This is the peak jitter. Thus the RMS number is 2.5/SQR(2)=700 psec

Have you got a chance to compare this XMOS to previous interfaces sonically? I am very curious to hear your opinion what isolation brings to the table as there are so many vague claims out there. BTW such an amazing blog you have, a wealth of knowledge and broad competence, impressive stuff indeed..thanks!

I have not compared this XMOS specifically, but I’ve experimented with isolators before, and in my setup I did not detect much differences. Check this: https://hifiduino.wordpress.com/2012/04/01/experiments-with-nve-il715-isolator/. The DIYINHK isolation is a bit different: in addition to isolating the I2S signals, the clocks are also isolated. This could be a benefit if using the clocks downstream (for example, for a reclocker board). In all honesty, I don’t have the ears to distinguish this level of improvements, but there is satisfaction from the engineering/diy point of view in that the “ultimate” in noise/jitter reduction can be accomplished, and especially at a very affordable price.

Hi, I have a B3SE with the previous DIYinhk non isolated USB/i2s interface, powered up by a Placid HD supply. I’m actually wondering if the Anamero would be a better choice to feed my DAC ? The DIYinhk is nice but I’d like real DSD…

On the other side the Anamero interface is an old design so I don’t know at all what to do… What do you think about that ? Thanks a lot

Yes, if you need to pass DSD, then use the Amanero. The Amanero is not an “older design”, just fully custom.

OK thanks for your answer and your work, perhaps a aku384 would be the best for me. I’ll see later .

What do you think of the latest Gustard U12 USB – uses the XMOS and crystal clocks. Just ordered one – very inexpensive. Nice PS filtering as well.

http://www.shenzhenaudio.com/gustard-u12-32bit-384khz-xmos-usb-digital-audio-interface-2014-new.html

Looks nice. Make sure they have the proper drivers for your platform

Hi this is Sam5050 -the fellow who did the ‘Reader Review’ of the Musilands. I posted above on the Gustard, it uses the generic XMOS Thesycon v1.6.1 ASIO drivers.

Which should keep getting updated and stay current.

Still love that Musiland 3.0 USB USD panel, and the drivers have been rock solid.

I like the active crystal clocks on the Gustard. They look to be very high quality. Also separate AC ps, with heavy filtering. Started a thread on HeadFi (rb2013).

They are cheap – I paid $159 shipped – off ebay.

Thanks again for the great blog – I’ve been reading up on the XMOS here.

Hello and thanks for continuing to share your projects here. Yeah, I continue to like the Musiland interface. The driver is indeed pretty rock solid. The only thing I “worry” about the XMOS is the way the clock frequencies are derived as explained a few posts above

Any word on the new Musiland products? Using their custom DSPs.

PS I’ll post my listening tests versus the Musiland 3.0 USD. Cheers!

On the XMOS clocking issue, I believe you described the clock derivation issue as:

“And according to this doc [link], the input clock (say the 24.576MHz clock) is sampled to the internal processor clock. Meaning that the external clock ticks (or transitions) are mapped to the processor clock ticks. This means that the worse “jitter” is when you just miss the external clock transition and must wait for the next internal clock tick. So the worse deviation from the actual frequency is the period of the processor frequency, thus for a 400MHz internal clock part, it is 2.5nS. This is the peak jitter. Thus the RMS number is 2.5/SQR(2)=700 psec””

Was this just a implementation of the XMOS on this particular DIYINHK board using the C7424Z chip, or is it implicit to designing around the XMOS? Sounds that way.

Although it was mentioned by HML that “The Xmos processor data sheets suggest that it may be possible to use the MCLK for the clock source for the BCLK and LRCLK. This is not done in the reference design and not in the DIYINHK board.”

I will post closeups of the Gustard U12 board when I get it.

I don’t recall completely, but I think this is inherent in the XMOS chip.

Thanks

Just discovered this – a shootout of 15 USB interfaces. The Berkley Audio Design Alpha won – they implement the XMOS. But it looks like quite a bit differently then DIYINHK. If you get a chance to checkout the boards – you comments would be appreciated. Thanks again.

http://www.computeraudiophile.com/f6-dac-digital-analog-conversion/15-universal-serial-bus-industry-standard-cables-connectors-and-communications-protocols-between-computers-and-electronic-devices-spdif-converters-shootout-15327/

The Berkeley interface is an isolated interface. Looks similar in design to the diyinhk isolated interface (https://hifiduino.wordpress.com/2014/01/24/diyinhk-isolated-xmos-usb-interface/) where the audio clocks and digital out are isolated from the XMOS chip. The isolators chips are different and of course, layout and power generation are done by different chips. And there is the “ferrite gate” thing…

In addition, the Berkeley interface outputs transformer isolated spdif signals whereas the diyinhk outputs I2S. There is a usb/spdif interface but non-isolated:

Thanks for the reply – well for $1800 I guess you should get something special. The reviewer speculates it a ADuM* isolator chip.

But as far as the clocking – it looks to be similar to the Gustard with crystal clocks, slaved to the processor clock.

The Silicon Labs isolators are lower cost than the Adums. I think there are 4 different companies that build isolators all based on different technologies. If it is the Adum, which is based on magnetic coupling, then the “ferrite gate” gizmo probably acts to “absorb” stray magnetic fields to prevent affecting other components. The Silicon Labs device is based on capacitive coupling. Whether or not the XMOS clocks can be operated in different ways, it is most likely determined by the firmware.

Recieved the Gustard U12. Sounds fantastic – better then the M2Tech Evo, Audiophilieo 2, or Musiland USB 3.0 USD.

Very natural sound, deep detail, great tone. A real steal for the money. Swapped out the Philips 2,200uf 25v caps for Pana FCs to improve ps rippled filtering.

Good to hear. Looking at the photos, there is an Altera FPGA in addition to the XMOS. Do you happen to know what are the functions implemented in the FPGA?

Not completely sure but guess it for DSD processing

The Gustard U12 (USB XMOS) is sounding amazing after some mods (upgraded ps caps and ERS shielding). For $155 a real bargain. I have a thread running – any mods you would suggest beyond that? Thanks for your blog – love reading it and have linked to it in my thread.

http://www.head-fi.org/t/736294/gustard-u12-usb-interface-8-core-xmos-chip

Yes, that is an “interesting device”. Would like to know whether the PFGA does reclocking. The XMOS is already capable of handling the USB side and in passing PCM and DSD data. The Musiland devices also use an FPGA, but they do not have an XMOS. I can see you’ve done extensive mods already…

In a way all devices that transfer data through USB do some sort of reclocking since the data coming through the USB has a different time domain. The Musiland reclocks the data with clocks generated by the FPGA clock management modules through clock division and multiplication and cascading. The XMOS reclocks the data by generating clocks based on its 400/500 MHz clock by “picking clock ticks that coincide with the external clock ticks”. It is possible that the Gustard uses the XMOS for its USB interface (and mature device driver) and the FPGA to reclock the data but based on simple clock division of external clocks rather than relying on its internal clock management circuitry. Based on most data sheets, the jitter originated from simple clock division is lower than the jitter originated from multiplication/division/cascading.

Have you had a chance to checkout this USB interface? I don’t see the C7424Z chip and three NDK clocks. Thanks! http://www.diyinhk.com/shop/audio-kits/54-xmos-192khz-high-quality-usb-to-spdif-with-ultralow-noise-1uv-regulator-wauto-power-switch.html

Yeah the clocks are there next to the XMOS chip. But I have not used that interface. Seems similar design as the other ones except it enables spdif

hi, i’m new here and also not an electronic expert. Hope somebody can help me

my usb interface (audio-gd NFB-1S) is broken (definitly). The manufacturer has discontinued selling usb interface (USB32, xmos or amanero) for my dac so i guess i got no other choice and deal with a diy solution.

1st of all can this interface (reviewed on this page) work with my and if so, how can i make it work ?

thanx, i’m stuck cannot listen to DSD and 384khz music

HELP!

abercrombie fitch