Amanero USB Synchronous Reclocking

Got inspired by the synchronous reclocking of the bitclock mod that was shared in the Amanero thread over at diyaudio. [link]. Very low cost mod that promises very high results. We are talking a few bucks to potentially drastically reduce jitter.

Here is the Potato Semi flip flop. Here I describe why I chose the Potato flip-flop [link].

Just got them in the mail (in a small hand-written envelope – unlike those large companies what would have sent FedEx in a huge box :-)). I purchased two just in case. It is a Dual Flip Flop (only one is needed), but they don’t come in single configurations:

I need power (3.3V), ground and bit clock from the Amanero board:

The 3.3V power supply from the Amanero board can provide up to 50 mA:

The Potato flip flop only consumes a miniscule amount:

Potato Semi flip flop on a SOIC to DIP adapter board. Unfortunately the only pin I could line up with the Amanero board is the bit clock pin to the input of the flip flop.

Made the necessary connections on the backside of the board: power, ground and the Q and Q-bar outputs for the flip flop. Yeah, no ground plane, but better connections would require a custom PCB.

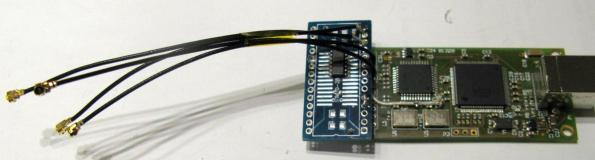

Mounted on the Amanero board, nice fit.

Used 0.1 uF film capacitor bypass close to the 3.3 V power pin (could be closer, but the Vcc and Gnd pins in the chip are diagonally opposite to each other):

The Clock signal for the flip flop can be tapped from R8 or R9. This is the native, low jitter master clock straight from on-board oscillators. One of the concerns is how to switch between the two clocks as both are needed. Fortunately it was reported that both clock lines can be tied together and connected to the clock input of the flip flop.

Apparently only one clock is active at any one time. By looking at the circuit diagram, the clocks have enable lines that are controlled by the CPLD and thus the CPLD can decide which clock should be enabled and which clock disabled. This is a very nice feature as it allows the re-clocking chip to use both frequencies and thus support both sample rate families: 44.1K and 48K.

I think I’ll make the connections to the two clocks like this:

Here is tapping the clock signals: (yes it is an antenna, but it is the shortest distance). The resistors are the smallest I could find in my recycle bin. Any small value should work I used 220 ohm resistors. The board uses 47 ohm resistors on the clock and data lines.

I have both the Q and Q-bar pins available. Right now it is connected to Q. Late I will use the Q-bar output and see what is the effect.

The entire module will be put in a metal case. That is why I had to reposition the OSCON capacitors. This will provide additional protection against EMI.

I think the box needs a logo or something to look “professional” 🙂

RESULTS

Works right away! and sounds pretty good.

I did a quick test on the different sample rates, 44.1, 48, 88.2, 96, 176,4 and 192 and they all work. I will later do my customary unlock measurement…

I must say, this has been a most satisfying mod.

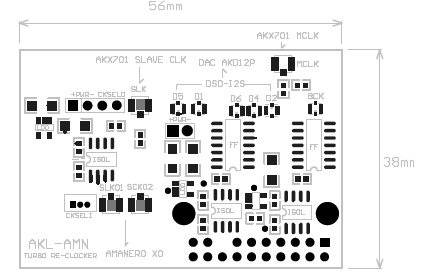

“PROFESSIONAL” MODEL

Here is a much better done mod by bigpandahk [link]:

PRODUCTION MODEL

Here is a board being developed by Acko [link]

Nice pics – very clear explanation. Curious to know – would it still sound better using a humble 74HC74 in place of the Potato chip? My suspicion is yes as FPGAs are notoriously bad for jitter…

Yeah, I am sure any “humble” flip flop would work. Just wanted to try the Potato Semi devices. They have several patents. And it was cheap to try.

Would this mod work in a “fully” sync mode (actually using MCLK from the Amanero to clock the DAC) or FSLCK and DATA would need the same Flip Flop treatement as BCLK?

I’m running a simple but chearful ES9023 based DAC in sync mode (no local XO for the sabre) from the Amanero and it sounds very nice.

Should work, the guy that posted the original mod on the diyaudio Amanero thread did just that: master clock to DAC and flip flop, reclocked flip flop to DAC

I just realized, what would happen when playing DSD with this mod? will it work?

It should work. The LRclock and Data becomes DSDL and DSDR and the bitclock becomes the DSD clock. LRclock and data are not reclocked so the DSD data remains the same. The bitclock works (in PCM mode) up to 192K which is half the master clock frequency.

I always think your smart wiring and soldering are really admirable!

I look forward to a report of unlock counting and of effect of Ian’s FIFO.

I am not sure about the soldering part. My “smart” wiring is because I like straight lines :-). But I think with some patience is needed in planning things out.

I started measuring the unlocks. This morning I ran it for 1.5 hrs and did not show any unlocks and this is the typical time where the Amanero would exhibit some unlocks. So it looks promising based on the little tests I’ve done. I’ll run it for a longer period and report back…

I connect pin 1,4,14 to Vcc, pin 7 to GND, pin 2 to BCLK and pin 3 to oscillator. Are my wiring correct? I can’t get any output from the flip-flop!!

The connections are correct. Are you using pin 5 as the output? Both pin 5 and pin 6 work for me. Pin 5 is good for 192K and pin 6 is good to 96K sample rates

Modern sofas

umowa zlecenie

Speak Spanish Greetings

for sale domains

Lunatik discount code

barrell head jig

Payday loans